Verilog vs VHDL

Introduction

Verilog and VHDL are two industry standard Hardware Description Languages (HDL) that are used in writing programs for electronic integrated circuits (ICs) i.e., ASIC and FPGA. Many system designers face this issue: which HDL language to choose – Verilog or VHDL. The answer is by no means easy or trivial. Both of these languages are widely compared and contrasted without any clearly defined victor. Both of them have their own merits and demerits and have different origins. Both of these languages hold major market shares of hardware description languages being used around the globe. It is difficult to say with certainty which one is better or superior; however, VHDL is older of the two. You can produce robust designs and comprehensive test environments with both languages, for both ASIC and FPGA.

History and Origin of Languages

Both Verilog and VHDL have originated from different programming languages and are supported by different schools of thought. VHDL is based on Pascal and Ada, thus characteristics of both of these languages are reflected by VHDL. Verilog, unlike VHDL, is based on C programming language and is relatively new as compared with VHDL. Internet sources claim that Verilog is supported mostly by the HDL programmers with industrial experience and background while VHDL is supported mostly by academic circles.

The development of VHDL was initiated in 1981 by United States Department of Defense (DOD) to address the hardware life cycle crisis. VHDL was developed for US Department of Defense (DOD) to provide a consistent hardware modeling language for documentation of digital hardware designs. It was never meant to design actual hardware; its sole purpose was hardware modeling. Since Verilog HDL was an intellectual property of Gateway Design Automation, which was eventually acquired by Cadence, so to maintain the supposed competitive advantage and distance themselves from any strategic ties to Verilog HDL to avoid any potential competitive control from Cadence, the individual Electronic Design Automation (EDA) companies extended considerable influence, resources and dollars to turn this language into a hardware design language. These same individual EDA companies developed and implemented their own semi-unique versions of the language at different stages of its development and implementation. The reason that these EDA companies did not adopt Verilog HDL is that they all have a basic philosophy which states that they must own all of their core technology which was being violated in case of Verilog as it, being intellectual property of Cadence, was not open to public domain. Besides this the EDA vendors wanted to break Cadence’s stranglehold on the software design tool and IC design market by pushing and promoting VHDL, which was an open language. VHDL became IEEE standard 1076 in 1987.VHDL was updated in 1993 and is known today as “IEEE standard 1076 1993”.As an IEEE standard, VHDL must undergo a review process every five years or sooner to ensure its ongoing relevance to industry. The first such revision was completed in September 1993.

Unlike VHDL, Verilog has originated from the commercial and industrial world. It was developed as a part of a complete simulation system, which may be utilized for describing digital hardware systems as well. Verilog HDL was launched by Gateway in 1983.Gateway was bought by Cadence in 1989.Cadence had recognized that if Verilog HDL remained a closed language as compared with VHDL the pressures of standardizations would force the industry to VHDL. So Cadence opened Verilog to the public domain in 1991 by officially publishing it. Verilog HDL became IEEE standard in 1995.

Salient Features of Languages

Some of the most widely compared and contrasted features of Verilog and VHDL are:

1. Concurrency : A common characteristic of both these hardware description languages is that unlike software programming languages like C, Java and C++ etc., both these languages are concurrent in their behavior and program execution, as these languages are meant to design and simulate hardware.

2. Predefined Constructs: As compared with VHDL, Verilog HDL has more predefined operators, predefined gates and predefined resolution functions. Verilog also includes don’t care notation.

3. Lower Level Modeling Capability: Verilog is better suited to modeling devices at lower level (i.e., Gate Level and Switch Level) than VHDL. This is why Verilog is deemed more efficient and appropriate for IC designing.

4. Modeling Primitive Capability: As compared with VHDL, Verilog includes convenient truth table syntax to model primitives. However, the VITAL packages in VHDL provide this feature.

5. High Level Modeling Capability: As compared with Verilog, VHDL includes more constructs (abstract data types and packages etc.) for high level modeling. This is why VHDL is considered appropriate for system level modeling.

6. Case Sensitivity: Unlike VHDL, Verilog is a case sensitive language.

7. Semantics: Both VHDL and Verilog have simulation-based semantics.

8. Compilation and Interpretation: VHDL is compiled, while Verilog is an interpretative language.

9. Simulation and Control Capabilities: Verilog defines a set of basic simulation control capabilities (system tasks) within language. As a result of these predefined system tasks and a lack of complex data types, Verilog users often run batch or command-line simulations and debug design problems by viewing waveforms from simulation results database. Unlike Verilog, VHDL does not define any simulation control and monitoring capabilities within language. These capabilities are tool-dependent. Due to the lack of language-defined simulation control command and because of user defined type capabilities, VHDL users usually rely on interactive GUI environments for debugging design problems.

10. Dynamic Memory Allocation: VHDL supports dynamic memory allocation (pointer types), while Verilog has no such feature.

11. Roots of Languages: VHDL is more readable and a strongly typed language with its roots from Ada. While, Verilog because of having its roots from C is more like C and is considered inherently sequential. Because of its affinity with C, Verilog is preferred by C programmers.

12. Lack of Constructs: Not all the constructs and operators are included in both languages. For example, unlike Verilog, VHDL does not have unary reduction operator. Similarly, unlike VHDL, Verilog does not have mod operator and concurrent procedure statement. So neither of these two hardware description languages is perfect.

13. Data types: Verilog has very simple data types, while VHDL allows users to create more complex data types.

14. Physical Types: VHDL supports physical types while Verilog does not support physical types.

15. Named Events: Verilog supports named events while VHDL does not support named events.

16. Enumerated Types: VHDLhas enumerated types (FSM modeling) while Verilog does not support this concept.

17. Associative/Sparse arrays: Verilog does not support the concept of Associative/sparse arrays,while VHDL partially supports this concept,which can be modeled in VHDL using access types.

18. Class/Inheritance: There is no concept of class/inheritance in both Verilog and VHDL.

19. Data Packing : Both Verilog and VHDL do not support data packing.

20. Conditional & Iterative Generation: Both Verilog (using if,if-else,case and for) and VHDL (using if and for) support conditional and iterative genration.

21. Superior Features of Verilog:

· Verilog has clearer distinction between register and nets. Nets are used to model electrical connections, while registers hold values and act as memory elements.

· Nets have strengths and delay properties which emphasize their physical aspects. The delay may consist of up to 9 values; a different value may be assigned for each transition 0, 1 or z and for each minimum, typical and maximum case. Such a delay attached to a net is added to the delay of each assigned statement. The net types include wire,tri,wand,triand,wor,trior,tri0,tril(resistive),supply0,supply1 and trireg (with charge storage).

· Primitive gates include and, or, xor & not.

· Verilog is concise and easier to learn as compared with VHDL. Unlike Verilog, VHDL is extremely verbose, which means it requires many characters to say something simple. This is why there are many different ways of saying the same thing in VHDL which makes it complicated and confusing. VHDL is exact in nature and difficult to learn. Verilog is deemed quicker to code and debug as compared with VHDL.

· Unlike VHDL, Verilog has fork-join block. This construct lets you have nested parallel sequential blocks inside each other. This is a very powerful feature which is sometimes termed as ‘multi-threading’. You cannot have this feature in VHDL unless you use explicit synchronizations between two different processes.

· Unlike VHDL, Verilog is not a strongly typed language and this is why a 32-bit bus may be connected with and 8-bit bus by just padding the extra bits. Verilog does not require additional coding to convert from one data type to another data type like integer to bit-vector. So it does not have to pay the performance penalty caused by strong type checking and the designer productivity is also expected to be high in this case.

22. Superior Features of VHDL:

· Unlike Verilog, the concept of packages in VHDL, library management and separate compilation makes it an ideal candidate for higher level system modeling. There is no concept of packages in Verilog. Functions and procedures used within a module have to be defined inside the same module and thus they cannot be shared by different modules. However, the concept of package in Verilog may be emulated by declaring and instantiating a fictitious module with functions and procedures. Verilog, unlike VHDL, does not support library management and separate compilation. This is why; Verilog requires all modules being used in same simulation must be written in the same file.

· Unlike VHDL, Verilog types are very restrictive and are specific to IC modeling (wire, supply0, supply1 etc.). Many abstract data types may be defined in VHDL while Verilog data types are predefined.

· Unlike VHDL, Verilog has no concept of configurations and it lacks generics and textio.

· Unlike VHDL, Verilog has no access types.

· Unlike Verilog, VHDL has extensive type checking feature; this is why many errors may be caught before synthesis and simulation.

· VHDL provides more details in assignment and application of individual cells and signals within FPGA, but this requires a much better understanding of the FPGA. As compared with VHDL, Verilog despite being much easier to learn is neither efficient in use of available cells nor does it necessarily generate the fastest running implementation from the components available in FPGA.

· Unlike Verilog, the verbosity of VHDL makes it self-documenting.

· VHDL semantics are unambiguous and VHDL based design may easily be ported from one tool to another. This is why race conditions are never a concern for VHDL users. Simulation semantics in Verilog are more ambiguous than in VHDL. Though this ambiguity in Verilog semantics, gives designer more flexibility in applying optimization but it can also (and often does) result in race conditions if careful coding guidelines are not followed. It is highly probable that a Verilog based design generates different results on different vendors’ tools or on different releases of the same vendor’s tool.

· The advantage of strong typing in VHDL is that the potential bugs in the design may be identified as early in a verification process as possible. Many problems that strong typing uncover are identified during analysis/compilation of the source code.

Global Market Trends

Internet sources claim that VHDL is used mostly in Europe, Korea and Japan. While North America, South-East Asia, India and South America mostly use Verilog HDL.

In order to avoid the potential delay that may be caused by integration of different fragments of design developed by different government contractors using their own proprietary software development tools, the US government mandated that all the products developed under government contract must use VHDL software design tool. This is why, in USA companies involved with government and defense related projects use VHDL for their embedded systems development, while companies involved with commercial projects mostly use Verilog for their projects.

The European Space Agency (ESA) is an organization with 14 European member states, and with Canada as an associate member. The purpose of ESA is to promote cooperation among the member states in space research and technology and their applications.ESA has played an important role in promoting VHDL in Europe as a standard Hardware Description Language for embedded systems development (i.e. ASICs and FPGAs etc.).

Google Trends for both HDLs

With Google Trends, you can compare world’s interest in your favorite topics. Google Trends also show how frequently your topics have appeared in Google News stories and in which geographic regions people have searched for them most.

Google Trends provides insights into broad search patterns. Google Trends analyzes a portion of Google web searches to compute how many searches have been done for the terms you enter relative to the total number of searches done on Google over time. The results are then displayed by a graph, termed “Search Volume Index Graph”. Located beneath the “Search Volume Index Graph” is the “News Reference Volume Graph”. This graph shows you the number of times your topic appeared in Google News Stories.

Below the search and news volume graphs, Google Trends displays the top regions, cities and languages in which people searched for the first term you entered.

The “Search Volume Index Graph” and “News Reference Volume Graph” of Google Trends for Verilog versus VHDL are shown in Figure 1 below:

Figure 1: Google Trends - Search Volume Index and News Reference Volume Graphs

The Figure 1 shows that, over all, over a period of time ranging from 2004 to present time, people around the globe have searched much more for VHDL as compared with Verilog. However, these searches for VHDL in particular and Verilog in general have gradually declined over this period of time. It may be noted that much more search queries were generated for VHDL as compared with Verilog over the period of time ranging from 2004 to 2007.While,the search queries generated by people around the globe for both Verilog and VHDL seem be roughly equal over the period of time ranging from 2010 to present time.

It is evident from Figure 1 that over the period of time ranging from 2004 to present time, Verilog has appeared more than VHDL in Google news stories.

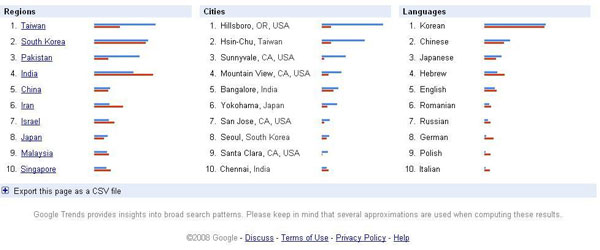

The regions, cities and languages in which people searched for Verilog as compared with VHDL are shown in Figure 2 below:

Figure 2 : Google Trends - Regions,Cities and Languages

Figure 2 shows a rough comparative overview of the countries, cities and languages in which search queries have been generated for both Verilog and VHDL. This Figure shows that overall in these regions, cities and languages shown VHDL was searched more than Verilog.

The figures and statistics shown in Google Trends portray that overall VHDL is more popular than Verilog as much more search queries were generated for VHDL as compared with Verilog.

It may easily be concluded from this article that both of these hardware description languages have their unique advantages and disadvantages and neither of them is perfect or ideal. The bottom line is that for ASIC designs, Verilog more closely defines the hardware. For higher level modeling, Verilog appears very limited because of the lack of packages and minimal type definitions (records, access and enumeration etc.).Anything that can be done in Verilog can also be done in VHDL; however the reverse does not seem possible. The HDL programmer is bound to adopt some engineering trade-off to meet his design requirements and should be familiar with both of these hardware description languages.

References:

1. http://www.angelfire.com/in/rajesh52/verilogvhdl.html

2. http://groups.google.com/group/comp.lang.vhdl/browse_thread/thread/

4bdeb69ef2f16dac/186b2b45950a74ff?q=VHDL++Verilog&rnum=10&pli=1

3. http://class.ee.iastate.edu/ee465/ee465s02/notes/billfuchs.pdf

4. http://www.bawankule.com/verilogcenter/contest.html.

5. http://au.answers.yahoo.com/question/index?qid=20110516233018AAvhDbO

7. http://inst.eecs.berkeley.edu/~eecsba1/sp97/reports/eecsba1h/verilog.html

8. http://www.deepchip.com/items/dvcon07-02.html

9. http://www.ece.msstate.edu/~reese/EE8993/lectures/verilog.pdf

10.http://stackoverflow.com/questions/4967493/does-anybody-have-quantitative-

data-on-vhdl-versus-verilog-use

11. http://trends.google.com/trends?q=vhdl,+verilog&date=all&geo=all&ctab=0&sort=1&sa=N

12. http://www.differencebetween.net/technology/difference-between-verilog-and-vhdl/

14. http://www.doulos.com/knowhow/faq/vhdl_faq/

15. http://www.google.com/intl/en/trends/about.html

16. http://www.google.com/trends?q=Verilog,VHDL

17. http://inst.eecs.berkeley.edu/~eecsba1/sp97/reports/eecsba1h/verilog.html

18. “Comparison of VHDL,Verilog and SystemVerilog”,Stephen Bailey,Technical Marketing

Engineer Model Technology http://www.model.com

19.The book "VHDL Designer's Reference",Jean-Michel,Kulwar Academic Publishers 1992.

- Comments

- Write a Comment Select to add a comment

To post reply to a comment, click on the 'reply' button attached to each comment. To post a new comment (not a reply to a comment) check out the 'Write a Comment' tab at the top of the comments.

Please login (on the right) if you already have an account on this platform.

Otherwise, please use this form to register (free) an join one of the largest online community for Electrical/Embedded/DSP/FPGA/ML engineers: