Doubt about constraining external input

Started by 3 years ago●4 replies●latest reply 3 years ago●117 views

Started by 3 years ago●4 replies●latest reply 3 years ago●117 viewsHi all,

I am usig an AD9914 DDS

https://www.analog.com/media/en/technical-documentation/data-sheets/AD9914.pdf

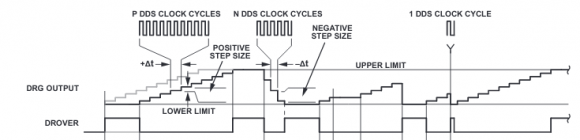

with its DROVER output connected to a I/O of the FPGA device (UltraScale+), used to signaling digital ramp as shown below:

Since this is an asynchronous non deterministic input signal, is it necessary to set timing constraints (e.g. input_delay) for the DROVER input to the FPGA ?

As far as I understand, input delay constraints make sense when setup and hold time with respect to a reference clock is known, input data and clk are running at the same frequency, but in this case the DROVER input is sampled at a frequency high enough to detect it. Would still make sense applying constraints ?

Thanks.

s.

The question should be: can the fpga input DROVER be asynchronous? I doubt it since it could be as short as one clock period of DDS yet needs to be seen by fpga. Thus you need to sync fpga with DDS clock and sample all inputs from DDS accordingly.

If the DRG time base is fsysclock/24 yes, DROVER can be sampled.

If you mean fsysclock is the fpga sampling clock and that it is related to DDS clock then that is ok for clock speed but you still need the input to be synchronous and not violate tSU/tH even if it is much slower, unless you don't want synchronous input in which case all clock details become irrelevant. alternatively use/think of FIFO transfer from DDS domain to fpga domain as any dual clock system.

No, I meant DDS fsysclock as datasheet reports.

In my case the DRG timebase would be around 104 MHz (DDS fsysclock = 2500 MHz).

I am actually using an edge detector to synchronize DROVER to FPGA clock.