How to understand -edge option if first edge of generated clock is falling edge?

Started by 5 years ago●1 reply●latest reply 5 years ago●130 views

Started by 5 years ago●1 reply●latest reply 5 years ago●130 viewsI am trying to understand the waveform created by create_generated_clock with -edge option.

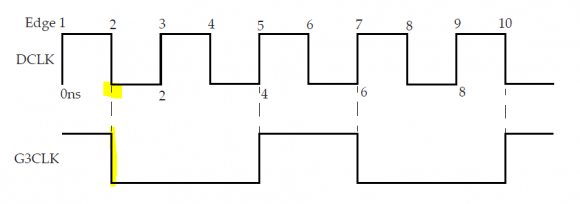

Suppose I have master clock as create_clock 2 [get_ports DCLK] like below:

I do create_generated_clock -name G3CLK -edges {5 7 10} -source DCLK [get_pins UAND0/Z]

Assuming needed is first edge of generated clock is falling edge, it is inferred at 1ns (or 2) automatically and why not at 3? Why would that be?

Suppose I have master clock as create_clock 2 [get_ports DCLK] like below:

I do create_generated_clock -name G3CLK -edges {5 7 10} -source DCLK [get_pins UAND0/Z]

Assuming needed is first edge of generated clock is falling edge, it is inferred at 1ns (or 2) automatically and why not at 3? Why would that be?

[ - ]

Reply by ●October 29, 2018

i think i misunderstand the diagram with edges. I suppose the 11th

edge is nothing but first edge, so from 10 to 11th edge is equal to high

period (1 step/1ns) and then 1 to 2nd edge (1ns) as another step which

makes positve 2ns, so the fall is at edge 2 and not 3. I hope this

understanding is correct.