An Editor for HDLs

Unless you're still living in the '90s and using schematics, your FPGA designs are entered into text files as VHDL or Verilog source. Which, of course, implies you're using some form of text editor. Now, right after brace placement in C, the choice of an editor is the topic most likely to incite a nerd civil war (it's a bike-shed issue). I won't attempt to influence your choice because it really makes no difference to me. But if you are using the same editor I do, then maybe I can help you use it more efficiently.

A poll on HDL editor popularity shows that Emacs is the winner by a wide margin with a 31% share, while vim and Notepad++ are tied at around 15% each. The remaining 39% is split between a hodge-podge of generic and IDE-specific text editors (e.g., the Xilinx ISE and Altera Quartus editors).

Emacs is most popular for good reason. It has powerful add-on packages that make creating and refactoring source code much easier. This includes packages for working with VHDL and Verilog code. It's also been widely ported, so you can use Emacs on just about any OS you'll encounter.

That said, I don't use Emacs. I had my love affair with it in the '90s but it just didn't work out. There were so many keystroke combinations involved in using it that I felt like I was casting strange incantations instead of entering code.

Over a period of years, I drifted through several Windows-specific editors like Zeus and Programmers File Editor. But I finally settled on Notepad++ as my editor of choice. Right out of the box it has:

- VHDL and Verilog syntax highlighting.

- Code folding.

- Block selection and column editing.

- Auto indenting.

- Configurable hot keys.

That's good, but it could be better. For VHDL and Verilog, I specifically needed templates, automated package declarations, and code beautification. Here's how I got those.

HDL Templates

If you're like me and you do a lot of things in addition to HDL coding, it can be frustrating trying to get all the syntax correct when you enter a new HDL module after being away from it for a while. Having a set of predefined templates for things like entities, functions, processes, etc. provides a strong code skeleton that I can flesh out with the appropriate I/O and signal declarations. Templates also help keep me consistent with the accepted HDL coding style. And filling-in a template is faster than recreating the code each time.

Notepad++ has a long list of plug-ins that extend its features. Several of these plug-ins, FingerText, NppSnippets and SnippetPlus, allow me to name and store blocks of code as snippets that I can later add to new source files with just a few key strokes or mouse clicks.

I chose FingerText because its macro language seems more powerful and flexible. Just typing module and a TAB into a file produces a VHDL entity and architecture with hotspots that the cursor will jump to so I can fill-in the entity name, inputs and outputs. Here is some additional information on using FingerText and a link to my set of VHDL snippets. You can modify and extend these snippets to match your own coding style, or create a new set for Verilog.

Automated Package Declarations

I always like to place a package body at the top of each VHDL file that contains the component declarations for any entities I've defined further down in the file. That makes it easy for me to instantiate these components in other VHDL source files without having to enter the component declaration in multiple places.

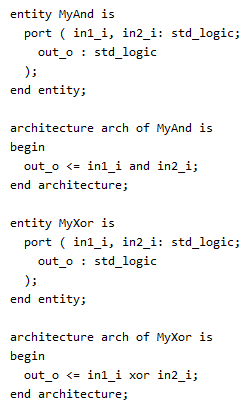

However, it's a pain to keep the component declarations in the package sync'ed with their associated entities as the input and output names are changed during development. So I developed a simple Perl script that manages this task for me and linked it to a Notepad++ hotkey. For example, if I enter a few entity-architecture pairs like these:

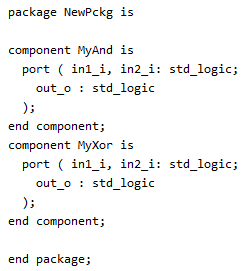

Then when I hit the hotkey, the following package is generated at the top of the file:

(Naturally, I change the initial NewPckg name to something more meaningful after the script runs.)

As I continue to develop the VHDL code in the file (e.g., adding/deleting I/O, creating/deleting new entities, etc.), the component declarations in the package body will be updated to reflect the changes each time I press the hotkey.

You can get my Perl script for generating packages here. Store it in a directory such as C:\bin, hit F5 in Notepad++ and then type the following into the Run... dialog:

perl C:\bin\vhdlpckg.pl $(FULL_CURRENT_PATH)Then click the Save button, associate the command string with a particular keystroke combination (I chose Alt-P), and assign the command a descriptive name.

Now when I have an open Notepad++ window with some VHDL code, hitting Alt-P will create/update the package with whatever changes I've made to the entities. (Just make sure to enable File Status Auto-Detection in the MISC. tab of Notepad++'s preferences so the updates are automatically displayed without manually reloading the VHDL file.)

Code Beautification

Keeping everything indented properly and using consistent formating are not big strengths of mine. Besides, my editor should be able to do these rote operations automatically, right?

Unfortunately, Notepad++ doesn't have a VHDL or Verilog beautifier, either built-in or as a plug-in. And I was unable to find a good, free, stand-alone HDL beautifier utility that I could link to a Notepad++ hotkey. Emacs has the vhdl-mode and verilog-mode macro packages that will do just what I want, but they're written in a Lisp dialect that I can't execute directly. So, what to do?

In this case, the best option is to use Emacs, but use it from within Notepad++. I can create a Notepad++ hotkey that runs Emacs in batch-mode to beautify the current file and then reload that file into Notepad++.

First, download and install Emacs. (This also installs the VHDL and Verilog macro packages by default.) Then I press F5 to bring up the Run... dialog and type in the following command:

C:\bin\emacs-24.1\bin\emacs.exe -batch $(FULL_CURRENT_PATH) -f vhdl-beautify-buffer -f save-bufferFinally, I save it and assign it to a hotkey like Alt-B. Now I can tidy-up my VHDL code with a single keypress. (Of course, make sure the File Status Auto-Detection option is enabled like in the previous section.)

If you have style guidelines that aren't met by the way the HDL beautifiers work out of the box, the easiest way to fix that is to start Emacs and then set the VHDL and Verilog mode formating options there.

Conclusion

If you don't want to use Emacs, Notepad++ is a good choice for editing HDL code in Windows. Using the three add-ons I've discussed makes it even faster and easier to enter your VHDL code. There's a lot more that could be done, so let me know your ideas!

- Comments

- Write a Comment Select to add a comment

Done and working!

Do you have any clue or suggestion to draw waveforms in asci inside the vhdl file?

www.hwdebugger.com

Roy

To post reply to a comment, click on the 'reply' button attached to each comment. To post a new comment (not a reply to a comment) check out the 'Write a Comment' tab at the top of the comments.

Please login (on the right) if you already have an account on this platform.

Otherwise, please use this form to register (free) an join one of the largest online community for Electrical/Embedded/DSP/FPGA/ML engineers: