I'd like to use Vivado in non-project mode, using makefiles and Tcl scripts. However, my chip is a Zynq-7000 SoC where Vivado needs to generate a module representing the processing system component with all of its AXI ports and other signals that go to the FPGA proper.

I know how to do that in project mode, but can't figure it out for the non-project mode.

Does anyone have any experience of that?

Any help would be much appreciated.

Thanks!

Hallo Kocsonya,

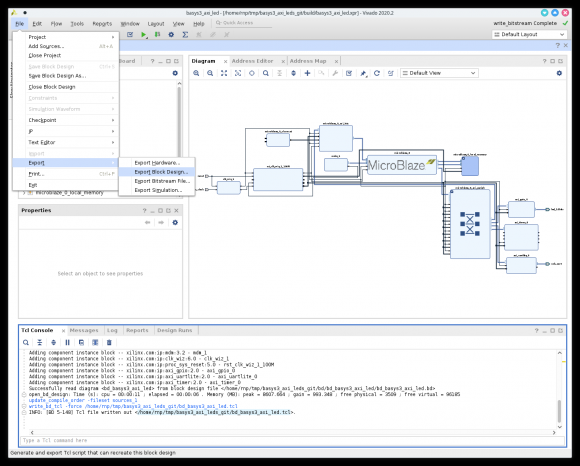

Vivado offers a way to this. Just follow te steps (see image below):

- Open the desired block design

- go to the menu: file -> export

- select "Export Block Design"

- vivado will open a new window and ask you to enter a name directory for the tcl file

Cheers,

Rafael.

Rafael,

Thanks for answering, but the point of the exercise is not to open the GUI. I know that method. The Tcl file it writes out is a project mode representation of the block design. That is, when you pass that Tcl file to Vivado, it will then create a directory with lots of files in it.

What I'd like to know if I can do that without opening the GUI. Have a Tcl file which creates just a single Verilog file which contains a module representing Zynq's internal ports to the FPGA and nothing else. No GUI, no project creation, no Vivado maintaining sources.

Thanks again,

Kocsonya

Hello Kocsonya,

You can use the generated tcl file to add the PS + AXI connections and IP, and you can just strip out the part related to the Vivado project.

Regards,

Rafael.