The Spartans

The latest release of the Xilinx Spartan family is the Spartan6 line of FPGAs. It has been awhile since the last major Spartan released, the Spartan3, but this last year Xilinx released the Spartan6. The Xilinx Spartan family is the low cost FPGAs compared to the higher cost and high performance Virtex family. The Spartan family is derived from the Virtex architecture with some changes to reduce the cost. The Spartan3 FPGAs were derived from the Virtex-II architecture. Since the Spartan3 release Xilinx has released the Virtex4 and Virtex5. Xilinx did have updates to the Spartan family, the 3E and 3A versions, but these were minor updates with no major architecture changes. The new Virtex6 line was released in conjunction with the Spartan6 FPGAs. In this post the basic building blocks of the Spartan6 architecture will be reviewed.

CLBs, Slices and LUTs, Oh My

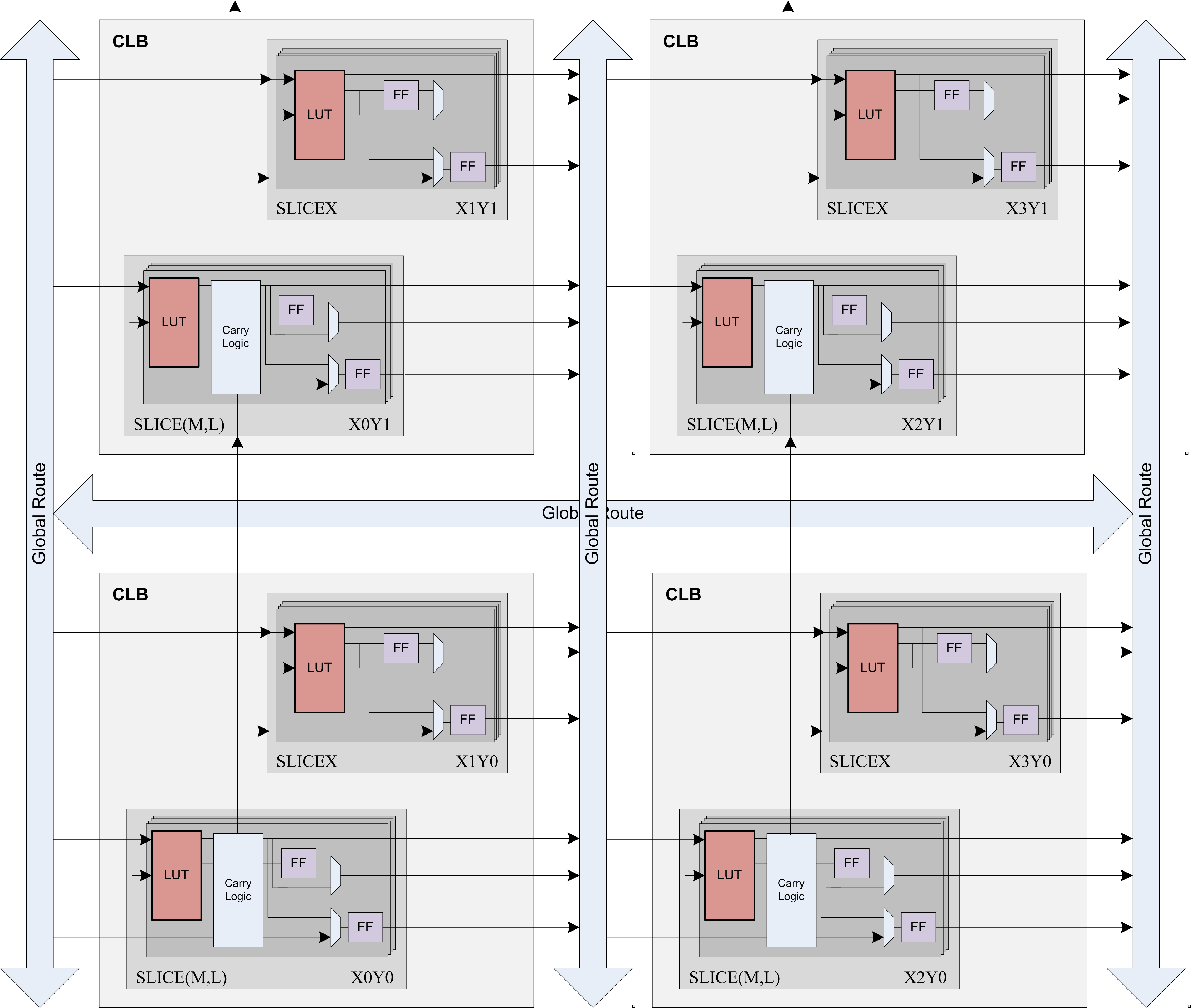

CLBs (Configuration Logic Blocks), Slices and LUTs (Look Up Tables) are the basic building blocks of the Spartan FPGAs. Figure 1 is a simplified schematic of the CLB, Slice, LUT and flip-flops. For more information see the Xilinx Spartan6 datasheet.

Configurable Logic Block and Slices

Configurable logic blocks (CLBs), as the name implies, are the logic building blocks and are organized in a grid on the chip. The CLBs are connected to the routing resources. The CLBs contain two Slices and the Slices contain 4 LUTs and 8 flip-flops. Slices also contain additional logic but the additional logic depends on the Slice type. The additional logic can include, a shift register, distributed RAM, etc.

Slices (SLICEL, SLICEM, SLICEX)

The base for a Slice is a LUT and two flip-flops as shown in 1. Each Slice has four LUT-FF pairs (total 4 LUTs, 8FF). The number and organization of the Slice types depends on the part, example XC6SLX9 has 1430 total Slices:

Note each CLB will have one SLICEX and either a SLICEM or a SLICEL.

LUTs

The Spartan6 devices introduce a new LUT configuration not seen by Spartans. Xilinx introduced the 6-input LUT (versus the previous 4-input LUT) in the Virtex5 architecture and now it is available in the Spartan6 FPGAs. Xilinx advertises that the 6-input LUTs utilization should be equal to 1.6 4-input LUTs. Roughly, every 3 4-input LUTs used in Spartan3 devices should only required 2 6-input LUT. A couple experiments were performed of real world designs to compare the 6-input LUT versus the 4-input LUT utilization. The gateware from USBP HDL and from OpenCores were mapped (timing driven mapping) targeted for a Spartan3E and Spartan6 devices. The results are shown in Tables 2 and 3.

|

The difference in this case is slightly greater than 10% (Spartan6 used 10% less LUTs than the Spartan3E). Two more designs were compared in tables 3 and 4. The Hilbert transformer design had a difference of 13% while the iterative product code decoder had a difference greater than 30%.

|

Based on the datasheet and the above experiments one would expect to use less LUTs in a design implemented on a Spartan6 but it is hard to quantify how much less. It would be safe to be conservative and assume a number of 10%-15% and hope for a better mapping than to expect a 30% increase.

Couple Notes, Xilinx started adopting the ``logic cell'' metric to quantify the resources available in a part versus the ASIC gate. This should make it easier to compare FPGAs with other vendors such as Altera. The experiments were all conducted with the latest version of ISE (at the time of writing) which was ISE 11.3.

Christopher 2010-02-15 Other Blog PostsMyHDL ASIC ProvenUSB-FPGA : Introduction- Comments

- Write a Comment Select to add a comment

how much clock frequncy is there in that?

To post reply to a comment, click on the 'reply' button attached to each comment. To post a new comment (not a reply to a comment) check out the 'Write a Comment' tab at the top of the comments.

Please login (on the right) if you already have an account on this platform.

Otherwise, please use this form to register (free) an join one of the largest online community for Electrical/Embedded/DSP/FPGA/ML engineers: