I have a pretty simple verilog project, in Lattice Diamond 3.11.

My top module instantiates an OSCH (Lattice IP library) oscillator at 133 mhz, and a 'ws2812b' module (my own) that drives a string of RGB Leds with a coloour pattern. Inside the ws2812b module I have a pulse-counter module (also my own), which basically divides the 133Mhz clock down by 4,000,000 to create a ~33hz clock. This low-speed clock is used to increment a simple counter which moves the colour pattern from one led to the next.

This is a pretty old project and it does work well. (see https://youtu.be/CwQ_p6rbQVg )

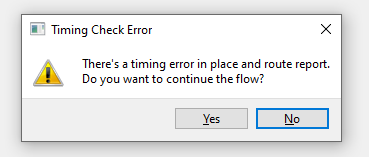

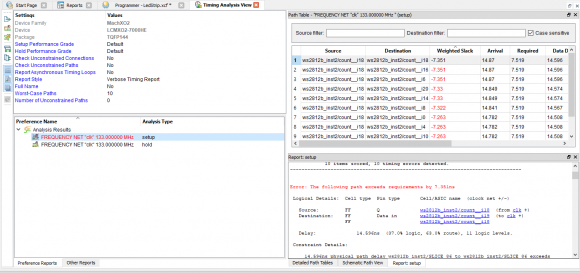

I updated to the latest version of Latrice Diamond recently, and now when I build the output files I get a timing error:

If I ignore the error and continur the flow, then the project still seems to work properly.

Any ideas?

you got setup timing violations (not exactly clock spec issue). I also notice you have gated the clock down to very low speed. My feeling is that your design is to blame. we normally keep the clock clean and if we have to divide it we use the divided slow signal as clock enable in order to wire the master clock to registers cleanly. In your case the slow clock is very slow but you still can use it as clock enable assuming your design can manage 133MHz speed. I think your timing violations are on the dividing counters at the high speed stage. You better check your clock division logic. and remember that even a very slow clock may also fail hold timing (not setup) if it is gated.

Thanks for the reply! Much appreciated.

I will look carefully at your suggestions - thank you!

Some more info: The MachXO2 has a built in dedicated clock generator but it can only give one output, so I run it at 133 Mhz. From this I need to derive all the other timing in the system, its running on an EVM with no other clock source for now. You are right about dividing down the clock, actually I don't divide it, but 'count' cycles and toggle a wire each time the cycle hits a predtermined count.

In order to get the low speed clock which moves the animation at approx 30 Hz, it has to count to a high number! (4.43 Million). Probably not the best way to do this!

what you described using counters is clock division and is common practice.

Your counter may be too wide (23 bits I guess) and thus fails timing on 133MHz clock. One alternative is using cascaded smaller counters until you reach desired output. You might also use plenty of power 2 small counters (modulo 2) and let each run freely(wrap around) without need to logic to clip at at some maximum value. for final rate you can employ a suitable counter.

to divide by 133*10^6/30 = 4433333.33333 you can use 2^22 + final counter and the 2^22 can be cascaded as smaller power of 2 counters.

The other option is use a single add 30 modulo 4433333 accumulator i.e. have an 23 bit adder and add 30 every 133MHz clock until it reaches 4433333 when you produce a single pulse. Still a wide adder just as it could be same as your counter anyway.

Thanks for those exceleent suggestions! I'll give it a try.